|

|

| ActiveWin: Reviews | Active Network | New Reviews | Old Reviews | Interviews |Mailing List | Forums |

|

|

|

|

|

DirectX |

|

ActiveMac |

|

Downloads |

|

Forums |

|

Interviews |

|

News |

|

MS Games & Hardware |

|

Reviews |

|

Support Center |

|

Windows 2000 |

|

Windows Me |

|

Windows Server 2003 |

|

Windows Vista |

|

Windows XP |

|

|

|

|

|

|

|

News Centers |

|

Windows/Microsoft |

|

DVD |

|

Apple/Mac |

|

Xbox |

|

News Search |

|

|

|

|

|

|

|

ActiveXBox |

|

Xbox News |

|

Box Shots |

|

Inside The Xbox |

|

Released Titles |

|

Announced Titles |

|

Screenshots/Videos |

|

History Of The Xbox |

|

Links |

|

Forum |

|

FAQ |

|

|

|

|

|

|

|

Windows XP |

|

Introduction |

|

System Requirements |

|

Home Features |

|

Pro Features |

|

Upgrade Checklists |

|

History |

|

FAQ |

|

Links |

|

TopTechTips |

|

|

|

|

|

|

|

FAQ's |

|

Windows Vista |

|

Windows 98/98 SE |

|

Windows 2000 |

|

Windows Me |

|

Windows Server 2002 |

|

Windows "Whistler" XP |

|

Windows CE |

|

Internet Explorer 6 |

|

Internet Explorer 5 |

|

Xbox |

|

Xbox 360 |

|

DirectX |

|

DVD's |

|

|

|

|

|

|

|

TopTechTips |

|

Registry Tips |

|

Windows 95/98 |

|

Windows 2000 |

|

Internet Explorer 5 |

|

Program Tips |

|

Easter Eggs |

|

Hardware |

|

DVD |

|

|

|

|

|

|

|

ActiveDVD |

|

DVD News |

|

DVD Forum |

|

Glossary |

|

Tips |

|

Articles |

|

Reviews |

|

News Archive |

|

Links |

|

Drivers |

|

|

|

|

|

|

|

Latest Reviews |

|

Xbox/Games |

|

Fallout 3 |

|

|

|

Applications |

|

Windows Server 2008 R2 |

|

Windows 7 |

|

|

|

Hardware |

|

iPod Touch 32GB |

|

|

|

|

|

|

|

Latest Interviews |

|

Steve Ballmer |

|

Jim Allchin |

|

|

|

|

|

|

|

Site News/Info |

|

About This Site |

|

Affiliates |

|

Contact Us |

|

Default Home Page |

|

Link To Us |

|

Links |

|

News Archive |

|

Site Search |

|

Awards |

|

|

|

|

|

|

|

Credits |

|

Product: Pentium 4 2.8GHz & Intel D845EBT

Motherboard |

CPU Architecture

| Table Of Contents |

| 1:

Introduction 2: CPU Architecture 3: SSE2 Instructions & P4 2.8GHz CPU Design 4: Intel i82845e Chipset 5: Intel D845EBT Motherboard 6: Intel D845EBT Sound Features 7: Synthetic Benchmarks 8: Games Benchmarks 9: Applications Benchmarks 10: Benchmarks analysis 11: Conclusion |

Note:

If you have already read our previous Pentium

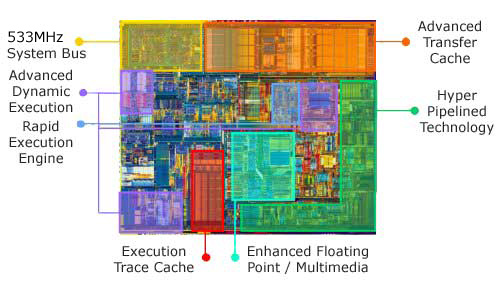

This gets complicated! Built on a P7

core engine, the Pentium

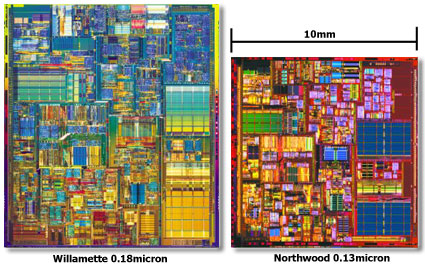

Intel Pentium 4 Willamette &

Northwood Dies

Even

though

using more pipelines present several advantages it has also a major

drawback: to handle the software instructions the processor tries to guess

which one will be the next using tests. With a pipeline enabled CPU the

instructions that follow the test should be managed before the processor

knows the test result in order to continually feed the pipeline. To know

which instructions should be used the CPU uses a ‘branch prediction’

mechanism: most of the time the CPU runs instructions it has already ran

before and probably knows the result ahead of time. It has a

But

in case of a test failure the whole BTB is trashed as well as all the

pipelines in order for the CPU to restart the operation: this process

obviously slows down the whole performance of the computer. The Pentium

For

those of you who don’t know an ALU is the name that was given to the integer

unit that manages math related operations like dividing, adding, multiplying

as well as logical operators like ‘OR’, ‘AND’, ‘XOR’, etc. Just like every

good superscalar processor worth of this name, the Pentium

Intel Pentium 4 Architecture

Schema

With

the

Trace Cache memory can store

As a

reminder Level

A new Bus: Don't Miss It

Over the months, the

The

Pentium